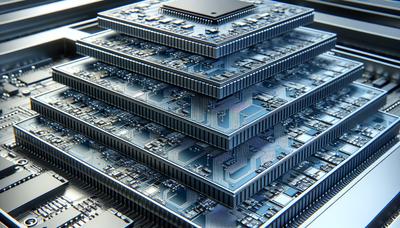

차세대 반도체: MIT, 실리콘 없이 다층 칩 기술 혁신 발표

Seoul전자 산업은 단일 칩에 담을 수 있는 트랜지스터 수가 한계에 도달하면서 어려움을 겪고 있습니다. 엔지니어들은 이제 반도체 구성 요소를 여러 층으로 쌓아 칩을 설계하는 데 주력하고 있습니다. MIT의 엔지니어들은 전통적인 실리콘 웨이퍼를 사용하지 않고 이러한 칩을 제작할 수 있는 새로운 방법을 개발했습니다. 이 새로운 방법은 칩의 데이터 처리 능력과 연산 성능을 크게 향상시키는 것을 목표로 하고 있습니다.

이 새로운 기술의 주요 특징:

- 실리콘 웨이퍼 기판이 필요하지 않음

- 400°C 이하의 저온 작동 가능

- 반도체 층 간의 직접 접촉 용이

- 현대 슈퍼컴퓨터만큼 강력한 AI 하드웨어 구축 가능성

향상된 반도체 밀도: 새로운 방식으로 가능해진 혁신

이 혁신은 전이금속 칼코겐화합물(TMDs)이라는 2차원 물질을 활용하여, 더 작고 성능이 우수한 트랜지스터를 만드는 데 유망한 기술입니다. 이러한 물질은 매우 얇게 만들어도 뛰어난 반도체 특성을 유지합니다. 이전에는 두꺼운 실리콘 층이 플랫폼으로 사용되어 층간 통신 속도가 느려졌습니다. 새로운 공정은 이 문제를 개선하여 칩의 반도체 밀도를 두 배로 늘릴 가능성을 제공합니다.

재료 과학 분야에서 중요한 발견이 이루어졌습니다. 연구자들은 용융 금속이 어떻게 결정체를 형성하는지를 연구하여 전이 금속 칼코게나이드(TMDs)를 성장시키는 새로운 방법을 개발했습니다. 이 신기술 덕분에 TMDs는 이전보다 훨씬 낮은 온도에서 생산될 수 있습니다. 따라서 이번 발전은 기존 온도 제한을 제거하고 집적 회로가 있는 칩이 제조 과정에서 손상되지 않도록 돕습니다.

엔지니어들은 다양한 TMD를 사용하여 n형과 p형 트랜지스터를 번갈아 배치한 다층 칩을 제조하는 방법을 개발했습니다. 이 기술의 발전은 칩에 더 많은 트랜지스터를 집적하고 각 층 간의 통신을 향상시킬 수 있게 합니다. 그 결과, 이러한 칩은 복잡한 인공지능 작업을 처리하고, 대형 데이터 센터처럼 효율적으로 데이터를 저장할 수 있습니다.

이 새로운 방식은 반도체 산업에 혁신을 가져올 수 있습니다. 엔지니어들은 이 성장 기반 3D 기법으로 만들어진 칩이 논리와 메모리 성능을 크게 향상시킬 수 있다고 믿고 있습니다. 미래에는 이 방법이 대규모 응용 프로그램에 활용되어 AI 칩의 생산에 영향을 미치고, 다양한 기술 분야에서 컴퓨팅 파워를 크게 증가시킬 가능성이 있습니다.

연구는 여기에서 발표되었습니다:

http://dx.doi.org/10.1038/s41586-024-08236-9및 그 공식 인용 - 저자 및 저널 포함 - 다음과 같습니다

Ki Seok Kim, Seunghwan Seo, Junyoung Kwon, Doyoon Lee, Changhyun Kim, Jung-El Ryu, Jekyung Kim, Jun Min Suh, Hang-Gyo Jung, Youhwan Jo, June-Chul Shin, Min-Kyu Song, Jin Feng, Hogeun Ahn, Sangho Lee, Kyeongjae Cho, Jongwook Jeon, Minsu Seol, Jin-Hong Park, Sang Won Kim, Jeehwan Kim. Growth-based monolithic 3D integration of single-crystal 2D semiconductors. Nature, 2024; 636 (8043): 615 DOI: 10.1038/s41586-024-08236-9

오늘 · 오전 6:48

심박 리듬과 아기 말소리의 새로운 관계: 조기 언어 발달 연구

오늘 · 오전 4:37

전통 끈놀이가 밝혀낸 문화의 연결 고리와 수학적 사고의 기원

오늘 · 오전 2:14

자외선 조사로 발견한 공룡 시대 익룡의 비밀: 새로운 연구 성과

이 기사 공유