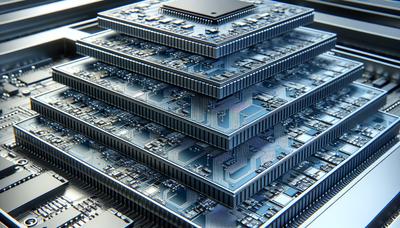

MITエンジニアが新技術!多層チップでAI性能を現代のスーパーコンピュータ並みに

Tokyoエレクトロニクス業界は、単一チップ上のトランジスタの数が限界に達しつつあるという課題に直面しています。 そこでエンジニアたちは、半導体部品を複数層に積み重ねたチップの開発に注力しています。MITのエンジニアたちは、従来のシリコンウェーハを使用せずにこれらのチップを製造するための新しい方法を考案しました。この革新的な方法は、データ処理能力と計算能力を大幅に向上させることを目指しています。

新技術の主な特徴には、以下が含まれます:

- シリコンウェーハ基板が不要

- 低温環境での動作が可能(400°C未満)

- 半導体層間の直接接触が実現

- 現代のスーパーコンピューターと同等のAIハードウェア構築の可能性

この革新技術は、遷移金属ダイカルコゲナイド (TMDs) と呼ばれる2次元材料を使用します。これにより、小型で高性能なトランジスタのための可能性が広がります。これらの材料は非常に薄くても優れた半導体特性を維持します。過去には厚いシリコン層が台座として使われ、層間の通信を遅くしていました。しかし、新しいプロセスではこれを改善し、チップ上の半導体の密度を2倍にする可能性を秘めています。

材料科学の研究者たちは重要な発見をしました。彼らは溶融した金属が結晶を形成する方法を研究することで、遷移金属カルコゲニド(TMD)を作り出す新しい手法を発見しました。この方法により、TMDをこれまでよりも低い温度で生産できるようになりました。その結果、以前の温度による制約が解消され、統合回路を持つチップが製造過程で損傷することを防ぎます。

エンジニアたちは、この手法を用いて、異なるTMDを使ったn型およびp型トランジスタを交互に配置した多層チップを作成しました。この進展により、チップにより多くのトランジスタを搭載することが可能になり、層間の通信も向上します。その結果、これらのチップは複雑なAIタスクを処理したり、大規模なデータセンター並にデータを効率的に保存することができます。

この新しい手法は、現在の課題を解決することで半導体業界を変革する可能性があります。エンジニアたちは、この成長ベースの3D手法を用いて作られたチップが、論理回路とメモリの性能を大幅に向上させると考えています。将来的には、大規模な応用でこの方法が活用され、AIチップの生産に影響を与え、さまざまな技術分野での計算能力を飛躍的に高めることが期待されています。

この研究はこちらに掲載されています:

http://dx.doi.org/10.1038/s41586-024-08236-9およびその公式引用 - 著者およびジャーナルを含む - は

Ki Seok Kim, Seunghwan Seo, Junyoung Kwon, Doyoon Lee, Changhyun Kim, Jung-El Ryu, Jekyung Kim, Jun Min Suh, Hang-Gyo Jung, Youhwan Jo, June-Chul Shin, Min-Kyu Song, Jin Feng, Hogeun Ahn, Sangho Lee, Kyeongjae Cho, Jongwook Jeon, Minsu Seol, Jin-Hong Park, Sang Won Kim, Jeehwan Kim. Growth-based monolithic 3D integration of single-crystal 2D semiconductors. Nature, 2024; 636 (8043): 615 DOI: 10.1038/s41586-024-08236-9

2024年12月20日 · 12:40

医療AIの公平性向上:STANDING Togetherが示す偏見解消と透明性推進の提言

2024年12月19日 · 17:19

AIによる予測、地球温暖化の深刻さが想定以上に:新たな研究が示す不安

2024年12月19日 · 15:09

AI革新で変わる患者ケア:強化学習と医療技術の未来

この記事を共有